2016年04月18日(月)

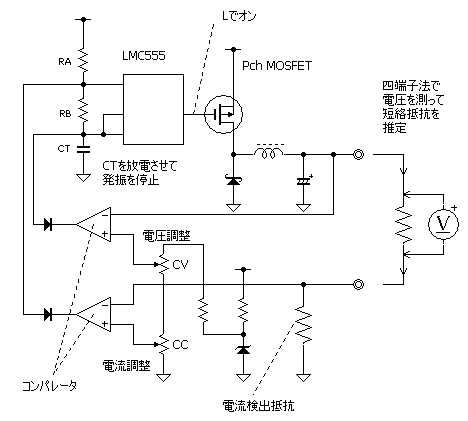

1A定電流電源回路ブロック図

|

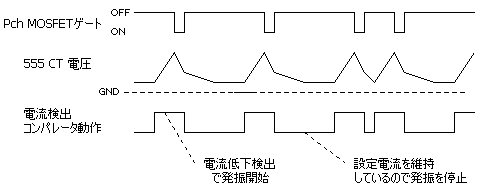

1A定電流電源回路の原理、こんな具合です。 (クリックで拡大↓)  CMOSの「555」を使い、「CT」を放電することで発振を 制御します。 電流検出抵抗は「0.1Ω」。 これに1A流すので、0.1Vが電流側コンパレータの検出 電圧です。 こんなタイミング図になります。 (クリックで拡大↓)  「RESET」端子のでの制御だと,CTは放電されるのですが、 出力が「L」になり、Pch MOSFETがドライブされてしまい ます。 CTを強制放電することで、出力にはHが出て、FETはオフ 状態になります。 「CV側」のコンパレータは、負荷が外れた(軽くなった) 時、出力電圧が不用意に上昇しないようするためのもの です。 検出電圧が低いステップダウン・レギュレータICって なかなかないんですよね。 ※NJU7620というのが、「電流センス基準電圧=0.2V」となっています。 |

2016年4月18日 10時43分

| 記事へ |

コメント(0) |

トラックバック(0) |

| ・電子回路工作 |

トラックバックURL:http://blog.zaq.ne.jp/igarage/trackback/4420/

※ブログ管理者が承認するまで表示されません

| ・電子回路工作 |

トラックバックURL:http://blog.zaq.ne.jp/igarage/trackback/4420/

※ブログ管理者が承認するまで表示されません

コメント